Estándar de memoria HBM4 revelado oficialmente — El doble de velocidad y eficiencia energética

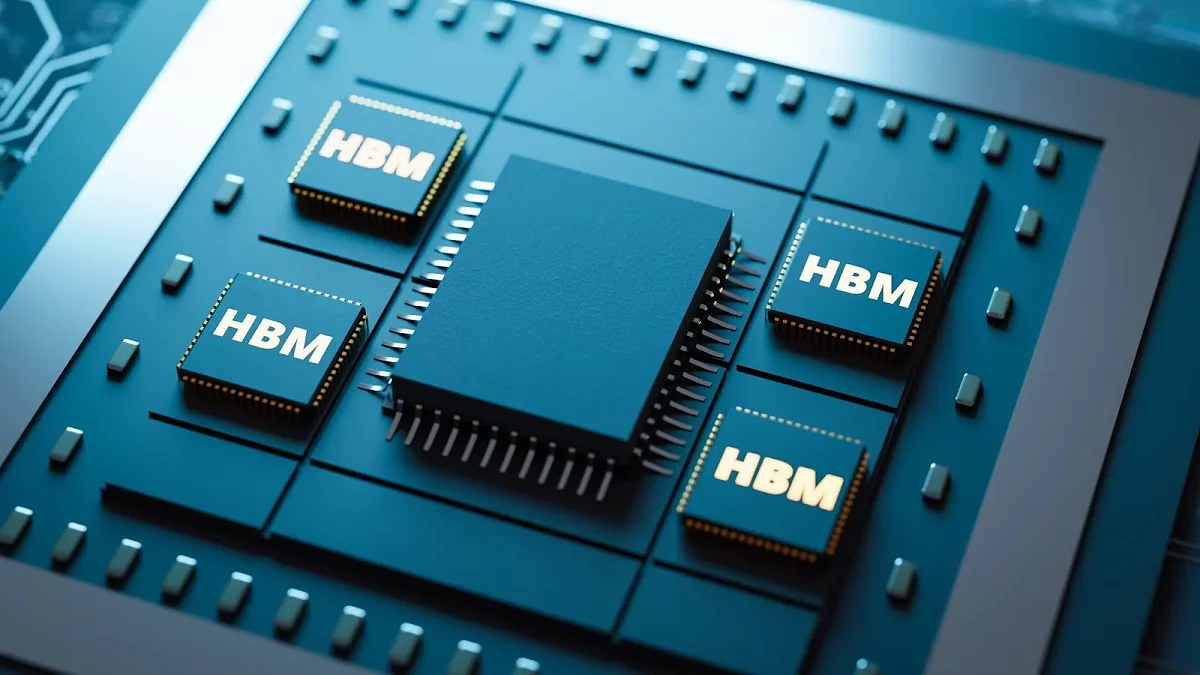

La Asociación de Tecnología de Estado Sólido JEDEC ha finalizado la especificación HBM4 — la próxima generación de memoria de alto ancho de banda. Diseñada para satisfacer las crecientes demandas de la IA, el aprendizaje automático y la computación de alto rendimiento, el nuevo estándar duplica el número de canales independientes por pila a 32, lo que permite un mayor paralelismo y un acceso a datos más flexible. Con velocidades de transferencia de 8 Gbps a través de una interfaz de 2048 bits, HBM4 ofrece hasta 2 TB/s de ancho de banda — un aumento del 60% en comparación con su predecesor, HBM3E.

La eficiencia energética se mejora mediante el soporte para múltiples dominios de voltaje (VDDQ y VDDC), lo que permite a los sistemas optimizar el consumo de energía según los requisitos de carga de trabajo. Para mejorar la fiabilidad, el estándar introduce la Gestión de Refresco Dirigido (DRFM), que ayuda a reducir el riesgo de errores de memoria. HBM4 sigue siendo compatible hacia atrás con los controladores HBM3, facilitando la transición a la nueva generación. Cada pila de memoria puede contener hasta 64 GB (16 capas de 32 Gbit), con configuraciones de 4, 8 y 12 capas también disponibles.

Los expertos estiman que la adopción generalizada de HBM4 en productos comerciales comenzará para 2026. Sin embargo, se espera que las primeras muestras de prueba lleguen a los fabricantes en los próximos meses, acelerando el desarrollo de soluciones para centros de datos, supercomputadoras y aceleradores gráficos. Se espera que HBM4 se convierta en una base para sistemas que requieren un rendimiento extremo — incluyendo IA generativa y simulaciones a gran escala. El estándar mejorado también puede ayudar a reducir el consumo de energía en los centros de datos al optimizar el manejo de volúmenes masivos de datos.