CPUs de próxima generación de Intel: la arquitectura de caché P-Core recibe una revisión, PCIe 5.0 tiene prioridad

El velo continúa levantándose sobre los detalles de la futura plataforma de escritorio Nova Lake-S de Intel, programada para 2026. Filtraciones recientes de informantes pintan un cuadro de cambios significativos tanto en los subsistemas de E/S como en la organización de la caché de la CPU.

Según la información que surge en foros de entusiastas, Nova Lake-S aprovechará en gran medida las interfaces modernas. Un aspecto clave es que la CPU dedicará 24 carriles PCI Express 5.0. Esto se traduce en beneficios prácticos: por ejemplo, un slot completo x16 puede manejar una tarjeta gráfica de próxima generación, mientras que los ocho carriles restantes permiten la conexión directa de dos SSD M.2 de alta velocidad a la CPU (cada uno utilizando un enlace x4). Se espera que el chipset añada otros ocho carriles PCIe 5.0, lo que potencialmente permitirá dos unidades M.2 PCIe 5.0 x4 más. Para la compatibilidad con componentes existentes, la plataforma también incluirá 16 carriles PCIe 4.0. Esto atiende a los usuarios que no están listos para saltar inmediatamente al almacenamiento de próxima generación más caro. En el frente de USB, las placas base prometen opciones extensas: hasta 14 puertos USB 2.0, hasta 10 puertos USB 3.2 Gen 2 (10 Gbps) y hasta 5 puertos USB 3.2 Gen 2x2 (20 Gbps).

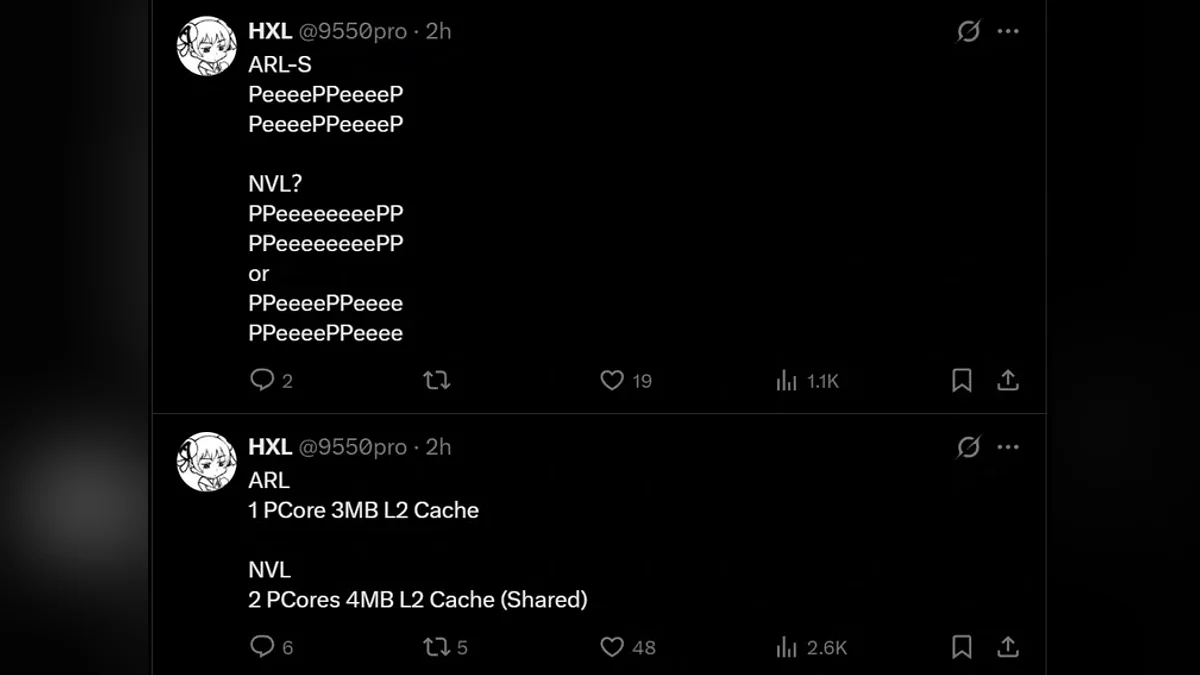

Filtraciones paralelas revelan importantes cambios microarquitectónicos. Los informantes indican que Intel está renovando la configuración de la caché de Nivel 2 (L2) para sus núcleos de rendimiento (P-cores). Alejándose del enfoque actual de Arrow Lake donde cada P-core tiene su propia caché L2 dedicada de 3MB, Nova Lake-S implementará una caché L2 compartida de 4MB para clústeres de dos P-cores. En una configuración de 16 P-cores de gama alta, esto significa ocho de tales clústeres, totalizando 32MB de caché L2 dedicada a los P-cores. Si bien este modelo de caché compartida basado en clústeres podría afectar la eficiencia del intercambio de datos entre núcleos vecinos, los detalles sobre su funcionamiento y las implicaciones de rendimiento permanecen en secreto.

Las discusiones también se centran en los posibles diseños para los bloques de computación dentro del chip. Las opciones bajo consideración incluyen colocar todos los núcleos de eficiencia (E-cores) entre dos clústeres de P-cores (un diseño de "sándwich") o alternar pares de clústeres de P-cores con clústeres de E-cores (una estructura "en capas"). La decisión final de Intel aquí aún se desconoce. Se espera que traiga cambios significativos tanto en la conectividad de dispositivos como en la estructura interna de la CPU, Nova Lake-S está lista para ser la plataforma de escritorio insignia de Intel para 2026.

- New Intel LGA 1954 Socket Keeps Dimensions, Cooling Compatibility with Predecessors

- Intel Docs Reveal First Confirmation of Nova Lake CPU Development

- Intel Arrow Lake's iGPU Smashed to 4.25 GHz in Insane Overclock

-

Nuevo zócalo Intel LGA 1954 mantiene dimensiones y compatibilidad de refrigeración con sus predecesores

-

Documentos de Intel Revelan la Primera Confirmación del Desarrollo de CPU Nova Lake

-

La iGPU de Intel Arrow Lake alcanzó los 4.25 GHz en un overclocking extremo

-

La GPU Battlemage de próxima generación de Intel ¿Aparece? Tarjeta PCIe 5.0 x16 detectada en la base de datos de PCI-SIG

-

Intel prepara el Core 5 120F para el zócalo LGA 1700